由于数2020欧洲杯预赛据中心被要求处理大量的非结构化数据,这些数据被输送到各种尖端应用程序中,fpga的未来看起来很光明。

That’s because FPGAs, or field programmable gate arrays, are essentially chips that can be programmed, after manufacturing, to act as custom accelerators for workloads including machine-learning, complex data analysis, video encoding, and genomics – applications that have far-reaching consequences for communications, networking, health care, the entertainment industry and many other businesses.

这样的应用程序使自己能够进行并行处理,并行处理是fpga的一个重要特性,它还可以随着这些工作负载的性质发展而动态地重新配置以处理新特性。

现在,赛灵思,这几十年来一直与竞争对手Altera公司(现在英特尔的部分)采用FPGA技术领导争先恐后,是揭幕它称之为一个新的产品类别 - 自适应计算加速平台(ACAP) - 即,它说,远远超出当前的FPGA的功能。

什么是ACAP?

Xilinx公司周一宣布,这类产品的第一个系列代号为Everest,将于今年推出(设计完成后),并于明年交付客户。这究竟是目前fpga的渐进发展还是更激进的发展还很难说,因为该公司发布的架构模型忽略了许多技术细节,比如芯片将使用何种应用程序和实时处理器。

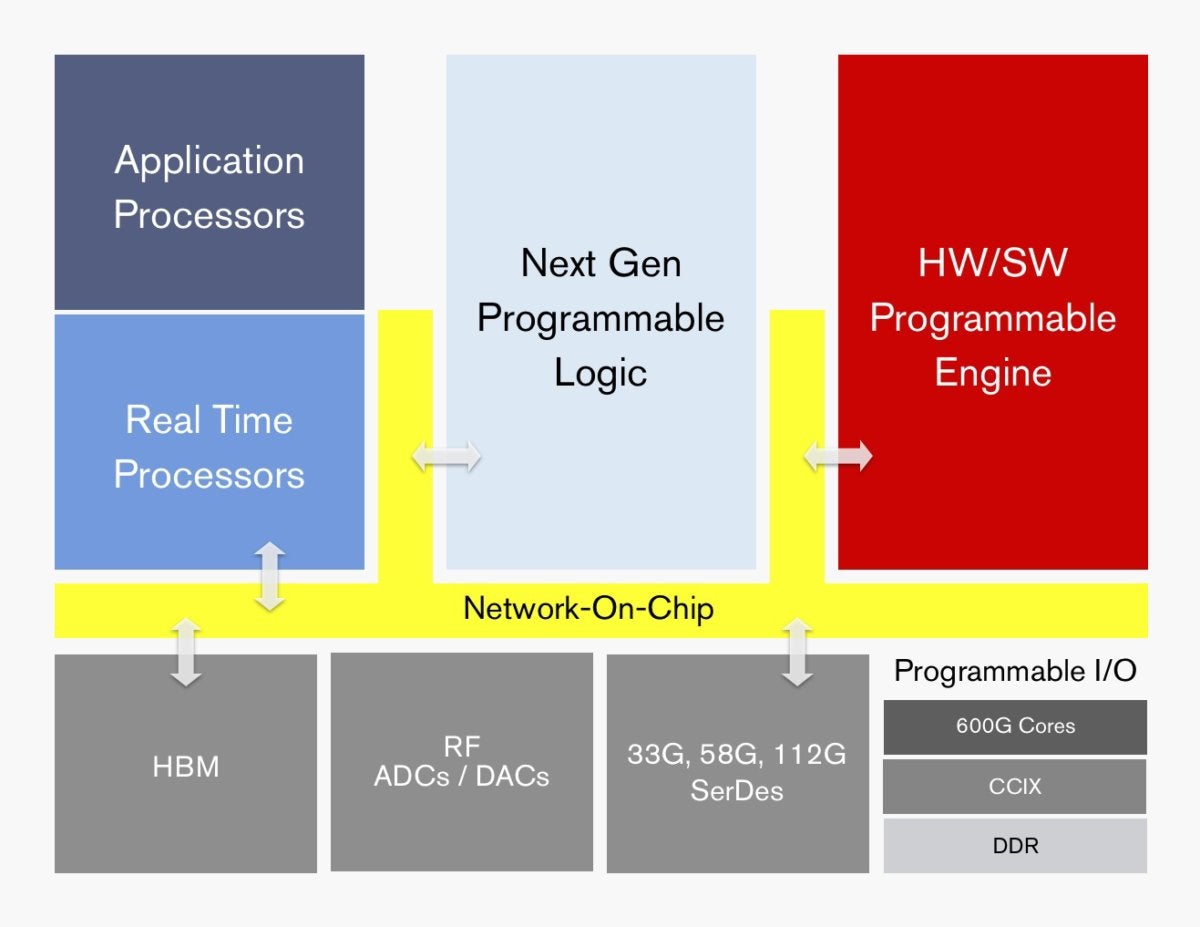

我们不知道的特点是必然的,虽然。珠穆朗玛峰将并入NOC(网络上的单芯片)作为标准功能,和使用(高速缓存一致性互连为加速器)互连结构,这两者都不出现在当前的FPGA中CCIX。

珠峰将提供硬件和软件编程,并随时成为市场上的第一集成电路的一个使用7纳米的制造工艺技术(在这种情况下,台积电)。越小制造工艺技术,更大的处理器上,这导致成本和性能效率的晶体管密度。

尽管关于生产工艺的命名以及英特尔和台积电生产工艺的相对优势存在争议,但其基本理念是7nm的几何尺寸大约是当前一代fpga的一半,每平方毫米的性能是它的四倍。Everest设备将拥有多达500亿个晶体管,相比之下,例如英特尔(以前的Altera)的电流的Stratix FPGA的10,它使用一个14nm以下的制造工艺和运动30个十亿晶体管。

赛灵思

赛灵思

Xilinx使用其ACAP技术的第一个产品系列代号为Everest,采用台积电工艺技术开发。

“我们真的觉得这是一个不同的产品类别,”最近被任命为CEO赛灵思维克多鹏说。赛灵思已经花费了约十亿美元在过去的四年里,并承诺1500名工程师到项目中。

赛灵思目前声称其FPGA,由于它们的能力被定制为不同的工作负载,加快了40倍,用于处理机器学习推理,对视频和图像处理的10倍和100倍为基因组学,相对于CPU-或GPU-基于系统。ACAPS,它说,将进一步加快AI了20倍推理,并通过4次超过其目前的FPGA架构5G通信。

FPGA的传统上提供经由可编程互连连接的可配置逻辑块的阵列。多年的FPGA重新配置是通过硬件描述语言(HDL)来完成,但芯片开发商已开始调整设备的架构,以便能够使用更高级别的软件编程语言。

赛灵思公司最近发布ZYNQ所有Programmable的SoC(片上系统)结合了已集成到产品中的基于arm的处理器的软件可编程性和FPGA的硬件可编程性。

“我们已经转换,但ACAP是拐点,如果你愿意,”彭说。“Even though before, FPGAs were flexible and adaptable, the level of that is much higher and yes, we started more recently enabling people to develop more at the software level, but the extent to which we’re gonna do it with this class of product is much higher. That makes this a quantum step over what we’ve seen before.”

使用高级软件编程语言

Xilinx说,软件开发人员将能够使用C/ c++、OpenCL和Python等工具与Everest合作。使用像Verilog和VHDL这样的HDL工具,Everest也可以在硬件、寄存器转移级别(RTL)上进行编程。

Moor Insights & Strategy的分析师Karl Freund认为,珠峰更多的是Xilinx战略的演变,而不是激进的一步,但他强调,珠峰在硬件和软件元素方面的进步是重大的。

“这是真的,那是一个新的类别,但它不只是使它成为一个新的类别的芯片 - 这是芯片,软件,图书馆,甚至是Web开发模式,”弗氏说。

他说:“他们在软件栈上投入了大量资金,所谓的加速栈使你能够更快速地部署FPGA解决方案,因为他们基本上提供了一些标准化的库、工具、算法和IP块,你可以挑选并部署在你的FPGA上。”

Xlinx说,除了一个尚未指定的多核SoC(芯片上的系统),Everest将提供PCIe和CCIX互连支持,多模式以太网控制器,用于安全和电源管理的芯片控制块,以及可编程的I/O接口。它还包括不同类型的SerDes - transceivers,转换并行数据到串行数据,反之亦然。具体来说,它将提供33Gbps的NRZ(不归零),58Gbps的PAM-4(脉冲振幅调制)和112G的PAM-4 SerDes。一般来说,PAM机制比NRZ提供更多的带宽。

Xilinx表示,某些Everest芯片还将提供高带宽内存(HBM),或可编程ADC(模数转换器)和DAC(数模转换器)转换器。

芯片上的,连贯的高速网络的主要区别

赛灵思说,FPGA和ACAPS之间的关键区别是NOC,其中装置的各种子系统连接,例如在多个处理器和I / O元件。截至目前的FPGA还没有系统级的国家石油公司,开发人员不得不主要通过芯片在可编程逻辑创建连接的基础设施。“你仍然可以通过编程可编程逻辑子系统但在一般情况下,你不会得到相同的性能特点,”彭说。

另一个关键因素是CCIX。“什么是革命性的,它的缓存一致的,”弗氏说。“这是第一次,你就可以建立与使用标准的网络协议,高速缓存一致性加速器的系统,而不会在任何地方行业现在存在的。”

CCIX是一套规范正由发达国家CCIX财团解决缓存一致性的问题,或者在尝试修改相同的内存空间或处理陈旧的数据副本时如何确保不同的cpu不会发生冲突。

珠峰的一大目标是AI。没有人期望珠峰背后英特尔CPU和NVIDIA GPU的纯粹的马力,这是被用来“训练”兆兆字节大小的数据集工作庞大,100级深,机器学习神经网络的竞争。

但珠峰的适应性,像传统的FPGA,非常适合“推理”,或实际上是把神经网络使用在现实生活中,弗氏笔记。这是因为神经网络的每个级别应与精度尽可能少进行处理,以节省时间和精力。不同于CPU,其中有固定的精度,FPGA的可被编程以处理的神经网络的每个级别,一旦其内置,与适合于该层中的至少精度。

边缘设备是主要目标

和而赛灵思说,它的主要目标是数据中心,边缘设备和的IoT可能最终是其中珠穆朗玛峰闪耀。2020欧洲杯预赛机器学习应用将越来越多地被纳入到边缘设备,这是非常功率受限相对于大型服务器,使他们FPGA的理想人选。

微软,这是第一个主要云供应商宣布的FPGA的部署公共云基础设施,去年给了芯片的信心一大票他们在AI使用,宣布将使用FPGA以其项目脑波深度学习的平台。它使用了来自Xilinx的宿敌Intel/Altera公司的stratix10 fpga,但这仍然有助于巩固使用fpga进行AI推理的想法。

赛灵思与英特尔之间的竞争不断将发挥出作为公司移动到更小的制造工艺技术。英特尔已经宣布了代号为Falcon Mesa的fpga,与英特尔10纳米制造技术,一些业内人士说,将提供相当于晶体管密度台积电7nm的过程来构建。

随着珠峰,并可能猎鹰梅萨由于出在2019年,它看起来像的FPGA - 或Xilinx公司的情况下,ACAPS - 将在计算比以往任何时候有趋势更为重要的作用。