DDR5内存规范是由于发布,但细节仍然稀缺。当JEDEC负责开发内存标准的组织时,遍布它是任何人的猜测。幸运的是,韩国的SK Hynix最近溢出了豆类,提供了一些扎实的信息。

DDR4或动态数据速率版本4在2014年出现。它以1600 MHz的速度开始,最终达到了3200 MHz,在高端,大多数DRAM在2000 MHz范围内。当时,这就够了。英特尔最好的Xeon处理器有八个核心,AMD很大程度上无关紧要。

快速前进到2020年。AMD彻底恢复活力和运输处理器64个核心,英特尔是发运28核芯片和承诺的48芯芯片。安培正在推广80核心臂服务器处理器,而Marvell则拥有一个96芯臂处理器名为Thunderx3。

突然,3200 MHz记忆不够。对于AI和机器学习的数据集,从而更大,记忆正成为真正的瓶颈。DDR5将解决这个问题。DDR5将从3200 MHz开始,随着时间的推移,缩放高达8400 MHz的方式。

Hynix计划所有DDR5内存至少在4800 MHz中运行,低于4800 MHz的速度将只是为了节省电力。这意味着DDR5内存在发射时比DDR4更大的带宽,只能更快。电力拉伸略微下降,从DDR4中的1.2伏特到1.1伏DDR5。

除了典型的速度和饲料改进之外,DDR5还通过称为“同一银行刷新”的东西来提高其性能。在DDR4中,所有内存库都必须同时刷新,即使只需要刷新DIMM上的16个内存库中的一个,如果它需要另一个银行的内容,则离开CPU等待。

使用DDR5,银行的数量加倍至32,但相同的银行刷新功能意味着内存存储体独立刷新,而其他银行则无法对系统访问。它是一个挤出更多性能并保持核心而不是等待的工具。

“关于DDR5的重要性是它提供的高水平集成,”Jim Handy,Harmalipal Analystist Analysis in Memory Analysis专门从事记忆市场的分析公司。“定义了这个规范的人利用了摩尔定法的事实,即摩尔定律不仅可以降低DRAM的每位的价格,而且它也使得增加筹码越来越强大的逻辑。他们巧妙地用它来改善CPU -DRAM带宽,移动记忆墙一个更远的东西。“

同样的银行刷新是一个很好的例子,方便说。“对于DRAM的整个历史记录,芯片无法在刷新时提供数据。现在相同的银行刷新允许在不进行刷新的银行中访问数据。这有很多可以改善数据通信。”

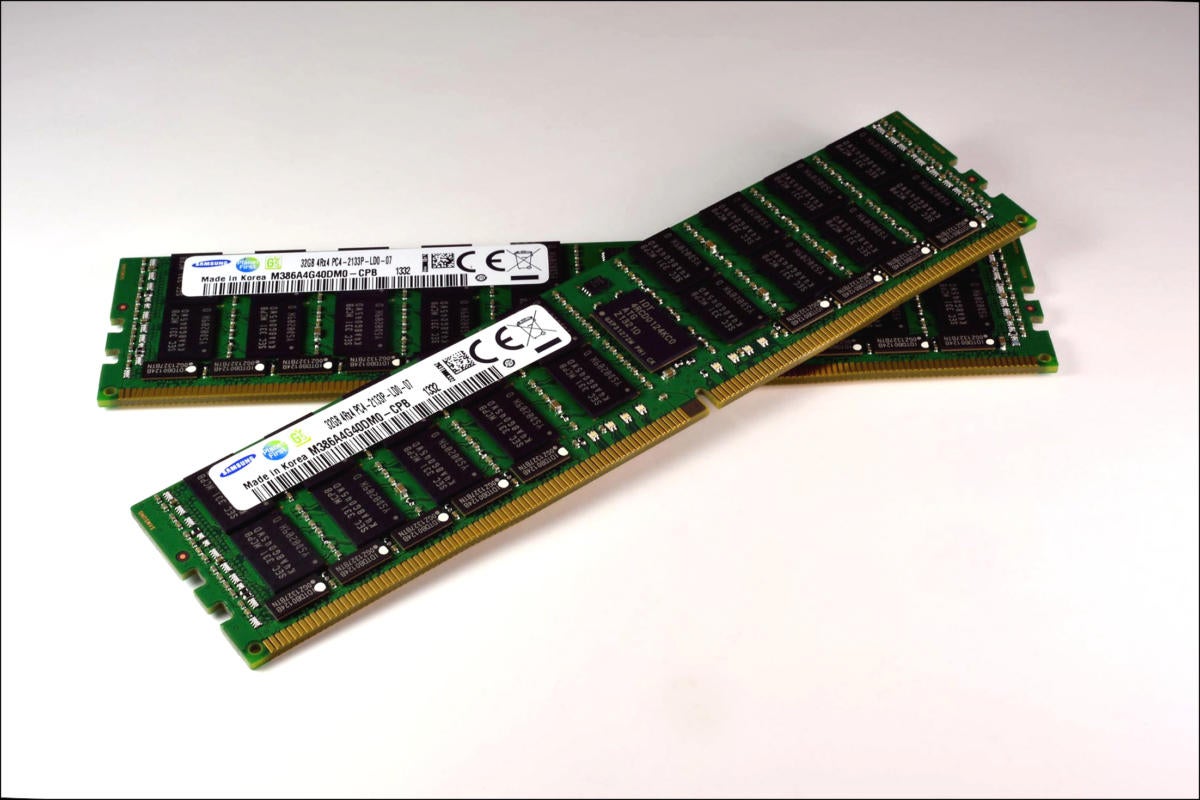

那么这个时候什么时候开始出现?去年,英特尔路线图被泄露给出现了英特尔计划搬到DDR5和PCI Express 5(完全跳过PCIe V4)的Hobbyist Rodmap泄露于2021年的PCI Express 5(完全跳过PCIe V4)。Micron已开始采样DDR5,Hynix表示计划在最后开始批量生产在今年,和三星计划明年开始DDR5生产。

这意味着我们可以预计2021年的卷产量增加,并且大众市场可能在2022年。我预计服务器将首先,只有桌面用户将受益于DDR5的变化。游戏玩家和超频器可能会在这些规格中流口水,但优先级可能是大铁,这迅速抵消DDR4的局限性。